觉得柔性电子就是可穿戴?那你就大错特错了

柔性电子技术的存在许多可能。

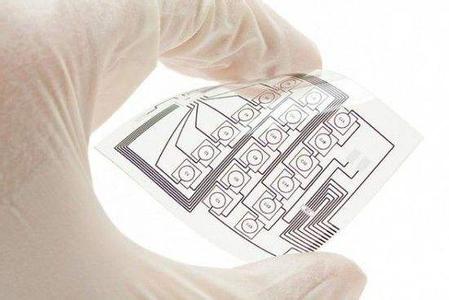

目前,业内针对从脉搏和活性监测到电解质平衡测量等各种应用提出了各种相应的柔性电子器件。这使得要将柔性电子设备泛化和通用化变得比较困难,不过,目前提出的各种柔性电子器件大部分都涉及到传感器、电源、板载数据存储器、分析性电子器件以及用于配置和数据传输的某种形式的通信部件的组合。

与刚性电子相比,柔性电子在成本和可用性上都具备一定的优势。(因此,本文将柔性电子和像智能手表这样的可穿戴电子产品区分开)。来自柔性电子产品的数据可能用于支持慢性疾病患者的治疗决策,所以准确和一致的测量至关重要。像皮肤一样弯曲和拉伸的贴片比尺寸更大、体积更大的器件的可穿戴性更好。而且,采用印刷电路技术制造的电子设备可能更便宜,如果出于卫生的原因需要把设备设计为一次性的,成本也是非常重要的一个考虑因素。

不过,随着应用的推广,柔性电子设备的灵活性和性能之间的矛盾和权衡很快就体现出来了。虽然在过去几年中,可印刷半导体技术取得了显著的进步,但是它们依然无法匹配先进硅片器件的高性能。基于此,许多观察者期望柔性电子设备使用混合技术,将非常薄的硅逻辑和通信电路和可印刷的传感器和可能的电源供应结合起来。

这种混合集成方案需要在不损坏硅电路的情况下将之转换贴装到柔性基板上。正如纽约大学的一名研究生Abdullah Alharbi在2016年12月份的IEEE电子器件会议上的演讲中所解释的,转换贴装技术分为三大类。第一类,强力方法,使用机械和/或化学抛光来薄化半导体。第二类,通过蚀刻等方法将外延层剥离,具体方法取决于将哪些嵌入的牺牲层选择性横向移除。

第三类方法,通过基板破裂进行机械剥离,也称为剥落。在受控剥落技术中,首先将具有高度断裂韧性和固有拉伸应力的亚稳定膜沉积到基材上。比如,在超薄绝缘体上硅(ETSOI)器件的顶部沉积预先拉伸张紧的镍。ETSOI这种材料非常理想,因为它的短沟道效应不强,使得设计者可以利用体偏置进行优化,并且不需要沟道掺杂。

接下来,使用一个柔性带拉动镍层,直到下面的衬底失效,在埋藏氧化物下方约20微米处开裂。这种方法的扩展性很好,而且是一个在室温下就可以操作的过程,适用于任何脆性基板。

应变工程是先进工艺流程中的一项重要特征,但柔性器件的应变工程几乎没有开展过任何研究工作。通过受控剥离,半导体从衬底释放之后会经历残余压缩应变。在GaAs中,这种残余应变可以用于调节带隙。例如,纽约大学的研究人员在制造用于能量收集的柔性GaAs太阳能电池的过程中,通过调节带隙,针对预期的光条件进行优化。

由于产量的限制,以及印刷电子器件需要较大的面积,全部采用印刷技术的电子器件可能最多只能容纳几百个晶体管而已,因此,混合电子技术很具有吸引力。最先进的印刷电路的线宽只能够能够做到几十微米。尽管如此,对于成本及其敏感的应用,比如用于医学检查的一次性传感器,印刷电子具有巨大的优势。非晶铟镓锆氧化物(a-IGZO)的载流子迁移率高达12cm 2 / V-sec,与多晶硅相当,是n型印刷半导体的主要候选者。不幸的是,根据Imec的Paul Heremans的说法,目前寻找互补p型半导体工作的进展有限。

迄今为止,p型半导体最好的候选材料是SnO,它的载流子迁移率为4.6cm 2 / V-sec。现在已经证明可以将SnO与a-IGZO在互补逻辑中进行集成,但是效果很差。SnO的缺点包括多晶结构和沉积膜中存在n型SnO 2和金属Sn。通过对候选材料进行原始演算筛选,(K,Na)2Sn 2 O 3、B 6 O和ZrOS也是很有希望的潜在替代物。然而,在进一步的模拟中发现,这些材料的非晶化会导致出现空穴。这样一来,这些材料不可能实现半导体器件所需的带状载流子传输。

大阪府立大学的Kuniharu Takei小组分别使用碳纳米管和溅射a-IGZO作为p型和n型半导体,Cr / Au电极作为源极和漏极。 聚酰亚胺提供钝化和应变弛豫层。在商用器件的球形灯中,碳纳米管薄膜晶体管表现出来的载流子迁移率为9.95cm 2 / V-sec。这种器件的通道为100微米长、400微米宽,为将来通过工艺收缩节约功耗和面积留下了很大空间。

正如在电子器件会议中的典型做法,这里讨论的器件只是一些原型以及对一些概念的可制造性证明。医疗传感器的发展道路还很长,面临商业应用时尤甚。然而,正如这些论文所展示的那样,现在正在出现一些技术平台,可以支持柔性电子技术的许多可能的不同用途。

【编者按】本文转自微信公众号:印刷电子在线

最后,记得关注微信公众号:镁客网(im2maker),更多干货在等你!

硬科技产业媒体

关注技术驱动创新

传感器

柔性电子

传感器

柔性电子

微信ID:im2maker

微信ID:im2maker

长按识别二维码关注

长按识别二维码关注