执念于“摩尔定律”的台积电,是时候为nm之路打造备胎了

半导体产业集体哀悼摩尔定律失效,坚持死磕会有未来吗?

台积电还是启动了2nm工艺的研发,工厂就设在中国台湾新竹的南方科技园。

从14nm、10nm、7nm、6nm、5nm、3nm再到如今的2nm,作为一个摩尔定律的疯狂追随者,台积电在制程工艺上是成功的,至少到目前为止是这样。

但如果加上半导体集体哀悼摩尔定律失效的大背景,再看台积电接下来每一步有关“nm”的布局,就让人难免感觉它是“过分执着”了。

从代工而来,制程工艺是技术转型的开始

台积电的成功,在于它几乎以一己之力奠定了台湾半导体代工产业的江山。

1985年,辞去德州仪器高管职位的张忠谋,受邀回台出任台湾工业技术研究院院长,次年便“创造性”的提出“台湾半导体产业,应当走代工之路”的思路,创立台积电,以3微米和2.5微米工艺制程切入市场,并几经波折拿到了英特尔的订单,一时间风头无俩。但同样出身工研院的联华电子却不干了。

和台积电相比,联电创立时间更早,曹兴诚还一口咬定代工模式是他想出来的,张忠谋只是抄袭者。随着台湾半导体产业在全球代工市场地位的提升,订单纷至沓来,产能滞后问题也逐渐暴露出来。在与联电的激烈竞争中,仅单纯依靠代工已经不可能再让台积电继续独占鳌头,只得另找出路,也就是技术转型。

背水一战之下,张忠谋斥资50亿美元买下了台湾的第三大晶圆代工厂,有着德州仪器众多技术大牛站台的世大半导体。基于此,台积电开始脱离“低级代工”模式,并于0.13微米工艺中打败联电。也就是从此时起,台积电开始在制程工艺上一骑绝尘。

有关台积电nm的进阶之路

在说台积电在制程工艺上的发展之前,我们先聊聊提升制程工艺的意义和技术难点。

简单来说,制程工艺越先进,集成电路的精度就越高,在同样的材料中可以承载的晶体管数量会越多、连接线越细。反应到芯片,就是性能越高、功耗越小。也因此对于IC厂商来说,越先进的制程工艺代工能够为其在日益激烈的竞争中赢得更多市场。

· 摩尔定律的完美执行者

其实在上世纪末,全球半导体产业中能在制程工艺上拥有话语权的只有英特尔,就连台积电当时都是靠着英特尔团队找出的200多个问题才得以顺利组成产线。

但三十年河东三十年河西,可能是在制程工艺上吃到了甜头,也可能是要将世大半导体的实力完全发挥出来,再加上从2000年前后全球半导体产业进入了飞速发展期,将摩尔定律奉为“神律”台积电从此走上了死磕制程工艺之路:

1999年,领先业界推出可商业量产的0.18微米铜制程工艺;

2001年,推出业界第一套参考设计流程,帮助客户降低0.25微米及0.18微米芯片的设计障碍;

2005年,成功试产65nm芯片;

2008年,率先批量投产40nm芯片;

2009年,28nm工艺试制成功,并于2011年实现量产,这也是台积电有史以来最成功的制程工艺;

2013年,20nm工艺实现量产,且拿到了苹果A8处理器的订单。

可以看到,随着技术和经验的积累越来越多,台积电制程工艺进阶的时间也越来越短,几乎将摩尔定律执行到了极致。但实际上,彼时的台积电即便进步飞快,在全球高端制程工艺竞争中也没能跻身第一梯队,直到16nm的出现。

· 和三星的较量

2015年,台积电宣布实现16nm制程工艺量产。原本,制程再次精进而广受行业关注无可厚非,但台积电这次“闹”的有点大。

因在A8处理器代工上的出色表现,台积电再次和三星一起拿到了A9的订单。有趣的是,这一次三星使用的是14nm FinFET工艺,而台积电用的则是16nm FinFET工艺。按照一般惯例,三星应强于台积电,但事实恰恰相反。

iPhone 6s上市后,大量用户在通过软件获取芯片信息后发现,三星和台积电的代工比例竟然是2:3。而更令人讶异的是,通过专业测试,搭载台积电代工的A9处理器的iPhone 6s,在功耗、续航等方面都强于三星,其中续航能力更是超出三星30%以上。一时间舆论哗然,“芯片代工”成为了那段时间的热议话题。

也就是从这里开始,台积电得到了苹果的重点关注,和三星的较量也进入了白热化阶段,最直接的就是它次年独吞了A10的全部订单。而更令三星焦躁的是,台积电的10nm很快就来了。

在移动智能终端快速迭代,性能要求越来越高的情况下,为尽快推出10nm,台积电在2014年启动了一项“令内部人员害怕”的计划——夜鹰计划,即重新编排所有研发人员,实施24小时三班轮值不停休工作模式。超高强度研发的推进下,2016年台积电宣布10nm开始量产,苹果的A11 Bionic、华为的麒麟970、联发科的HelioX3等大订单纷至沓来,到2017年第四季度,该制程工艺的营收占比已达台积电总营收的25%。

当然三星也没有示弱,在10nm制程工艺上推出了两个版本,10nm LPE(Low Power Early)和10nm LPP(Low Power Plus),除了应用在自家的Exynos 9810、Exynos 8895、Exynos 961上外,还拿下了高通骁龙835和845的订单。至此,制程工艺竞争来到了个位数阶段,其中以当下正在应用的7nm最为激烈。

2017年,台积电率先试产7nm制程工艺,次年宣布实现量产,进度快了三星超一年半时间。也因为此,A12 Bionic、麒麟980、AMD Zen 2均选择了台积电,就连高通都将骁龙855代工交给了它。

与此同时,麒麟985/990、苹果A13等也都被台积电纳入囊中,而以华为和苹果手机当前的市场占有率,台积电接下来的财报必然可观。

吃了个大亏的三星只能“打快”,赶在去年10月宣布可实现7nm EUV量产。与此同时,凭借低价,三星抢下了英伟达下一代GPU大单,产业链也有传闻称高通已重归三星,二者将就骁龙865展开合作,预计在今年年底前实现量产。而就在本月初,三星抢先推出了全球首颗采用7nm EUV工艺制程的Exynos 9825芯片,着实刷了一波存在感。

更值得一提的是,在有关“7nm EUV良品率导致高通芯片全废”假新闻的回应中,三星表示“今年4月已实现该工艺量产,第四季度将有相关5G产品量产。”

可以说,在7nm制程工艺代工上,台积电和三星正在“你追我赶”的博弈中,推动着全球半导体产业发展。但死磕制程工艺,真的是半导体产业一定要走的路吗?

质疑声起,台积电已经走入死胡同?

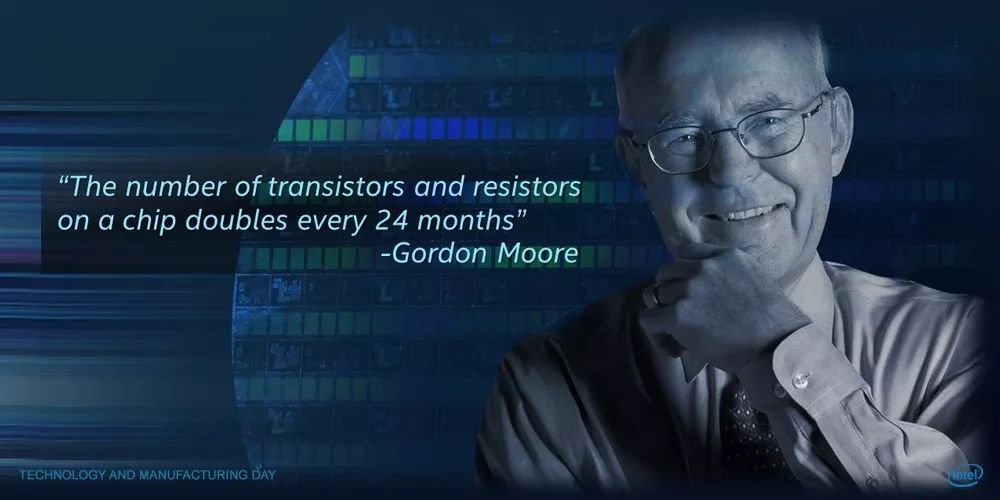

其实,早在制程工艺走到10nm时,有关“半导体工艺已达物理极限”的说法就开始在业内被广泛提及。当“撑到”7nm时,这种说法更是甚嚣尘上,毕竟就连英特尔都在这上面栽了跟头,黄仁勋更是公开表示“摩尔定律已失效”。

但显然台积电并不这么认为,其全球营销主管Godfrey Cheng最近就公开表示,“我们能够在工艺、制程、晶体管等多方面提升芯片性能,以延续摩尔定律。”

但显然台积电并不这么认为,其全球营销主管Godfrey Cheng最近就公开表示,“我们能够在工艺、制程、晶体管等多方面提升芯片性能,以延续摩尔定律。”

按照公开信息,接下来台积电将于明年试产6nm、用5nm制程工艺量产骁龙875、2021年投产3nm、2024年投产2nm,甚至预计在2050年将晶体管做到0.1nm。

然而,台积电真的能将nm制程撑到底吗?

其实,如果仅从制程工艺先进性上看,英特尔的10nm是要强于台积电的7nm的,前者晶体管密度达到了100.8MTr/mm2,而后者只有96.5MTr/mm2。也就是说,英特尔可以在一平方毫米的硅片中装入超一亿个晶体管,简直细思极恐。

而前文说到半导体工艺其实是存在物理极限,其中仅量子隧穿和寄生电容暴涨问题就极难解决,前者是当晶体管尺寸缩小到原子级别后,电子可能会随意穿过壁垒导致漏电的问题;后者则是在线路过密过细的情况下,出现非设计电容暴涨问题,导致功耗增加。或许也正因为此,英特尔一直没能实现10nm量产。

同样的问题台积电也需要面对,相较于死守制程工艺,多做两手准备更为实际,例如在材料、光刻、封装上下功夫。

材料方面,寻找新材料制作晶体管将是未来降低制程的主要途径之一。就当前来看,有关于3nm制程工艺的芯片材料均不是二氧化硅,而是石墨烯等新型复合半导体材料,但仅限于实验室阶段,量产尚需时日,例如美国劳伦斯伯克利国家实验室成功用纳米碳管制成了1nm晶体管。

光刻方面,光刻机决定了制程工艺最小尺寸。众所周知,光存在衍射问题,任何一台光刻机所能刻制的最小尺寸,与它所用光源波长成正比,即波长越短,尺寸就越小。就目前来看,EUV(极紫外)为所有已应用的光刻技术中最为先进的,而关键技术则只掌握在荷兰的ASML公司手中。也因此,应用更短波长的光源和掌握核心技术也将成为全球半导体产业未来的重要课题。

封装方面,张忠谋也曾说过,“为延续摩尔定律,先进封装也是可走的路。”目前,台积电已经推出CoWoS、bumping、InFO等后端3D封装产品和前道3D封装工艺SOIC和全新的多晶圆堆叠等多种封装方式。

以智能手机为例,在电池体积短时间内无法减小、芯片二维空间固定的情况下,适当增加芯片厚度,即“通过多加几层硅片以增加晶体管数量”不失为办法之一。

毋庸置疑,提升制程工艺为半导体产业发展提供了极大的助力,但在“物理极限”的挑战下,固守必定不是长久之计。作为全球首大晶圆代工厂,台积电在坚持按摩尔定律走下去同时,适当开辟一些“岔路”才能有备无患。

最后,记得关注微信公众号:镁客网(im2maker),更多干货在等你!

硬科技产业媒体

关注技术驱动创新

X

产业

手机

用户

移动

X

产业

手机

用户

移动

微信ID:im2maker

微信ID:im2maker

长按识别二维码关注

长按识别二维码关注