2nm芯片应该怎么造?台积电给出“终极答案”!

为了延续摩尔定律,科学家们想尽了方法……

随着先进制程下发热和漏电现象愈发难以控制,各家芯片巨头都在寻找新的工艺突破。

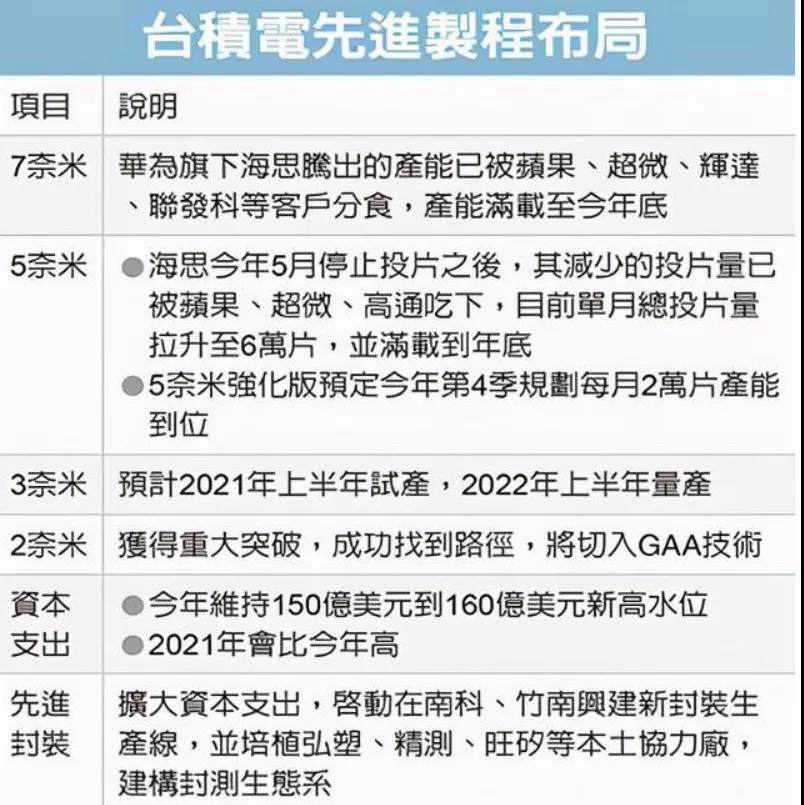

在最近举行的一场半导体行业大会上,台积电南京公司总经理罗镇球介绍了2nm制程的最新动态。

图 | 源自网络

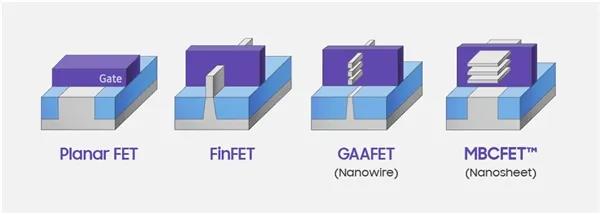

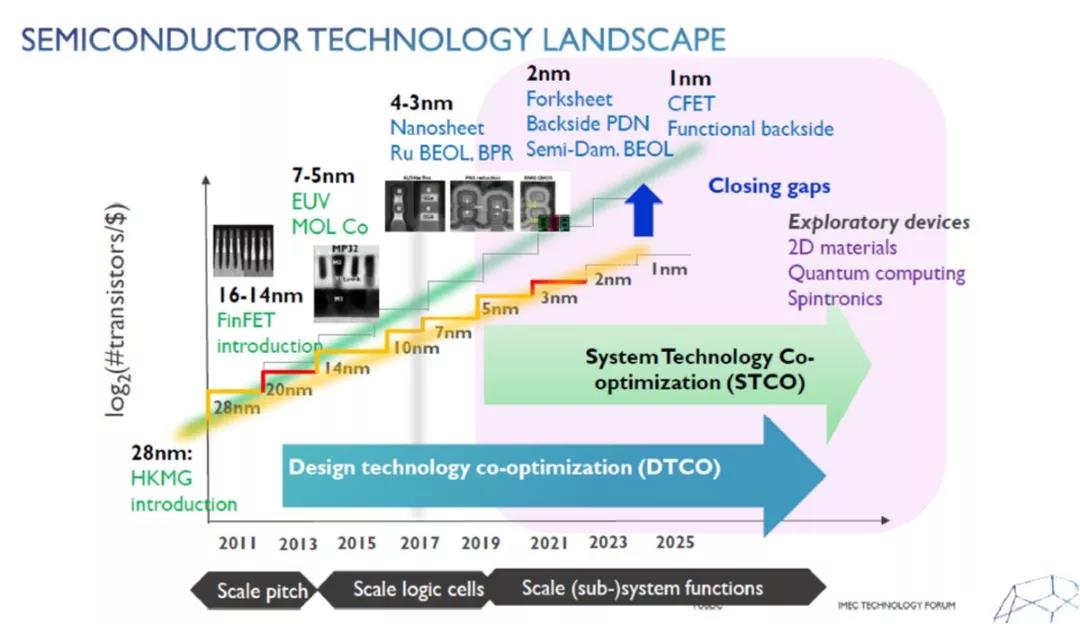

罗镇球表示,台积电将在2nm节点使用全新的nanosheet/nanowire(纳米片/纳米线)晶体管结构取代目前主流的FinFET工艺。

有趣的是,三星在3nm节点就已经采用新工艺,但因为制造技术难度大,量产计划被迫推迟,有点“起了大早,赶了晚集”的意思。

如今,两家半导体巨头将在2nm节点迎来一次“正面交锋”。

放弃FinFET,新工艺挑战摩尔定律极限

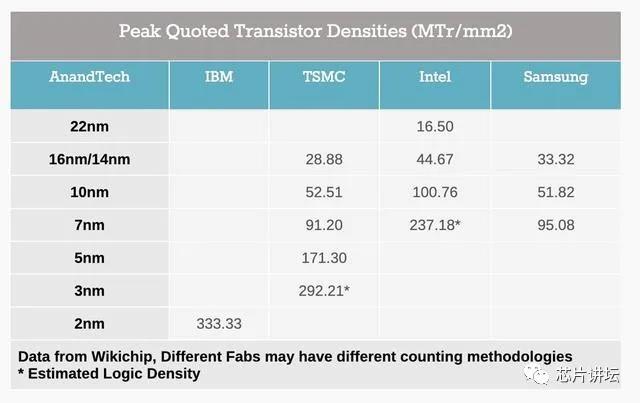

2nm工艺有多夸张?

按照台积电的说法,要在指甲盖大小(100mm²)的芯片上安装490亿个晶体管,这听上去就如同天方夜谭。

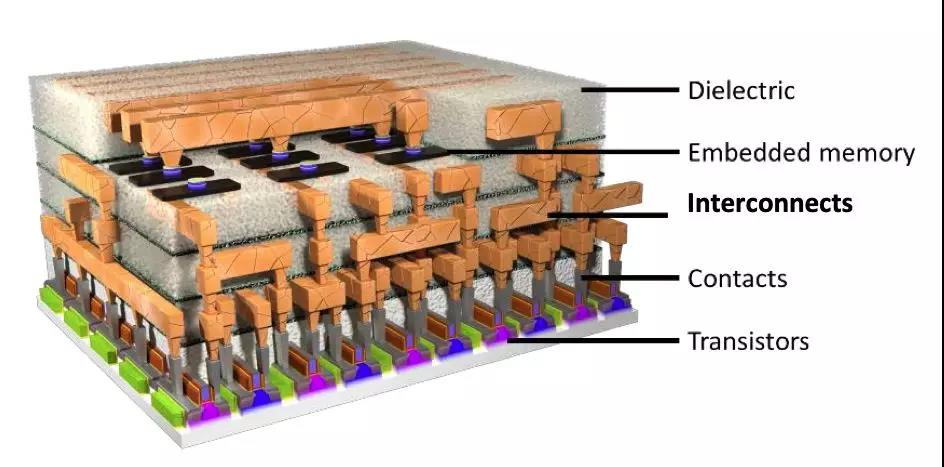

但工程师们总有新办法:如果能将晶体管像积木一样堆叠起来,那么就能有效减少电路的占位面积,那么晶体管的密度或许就能翻倍。

这种设计思路广泛被下一代新工艺采纳,例如此次台积电采用的nanosheet、英特尔主导的nanowire以及三星采用的GAA工艺(Gate-All-Around,全环绕栅极晶体管),本质上都大同小异。

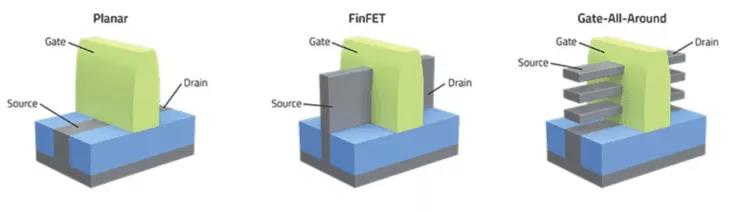

用一个简单的例子来描述新结构:在最早的Planar工艺下,半导体材料如同一张2D平面的白纸;到了FinFET时代,这张白纸被折成了3D的鳍(Fin)状,缩小了闸长。而如今为了放下更多晶体管,半导体材料像积木一样被堆叠起来,就如同高楼大厦一样立体,最终可以容下更多晶体管。

除了解决晶体管密度问题以外,新工艺另一个目的是为了解决高温以及漏电(leakage)现象。

在2nm节点,集成电路的线宽接近电子波长,精细程度几乎达到了原子级别,理论上量子隧穿效应已经来到物理极限。

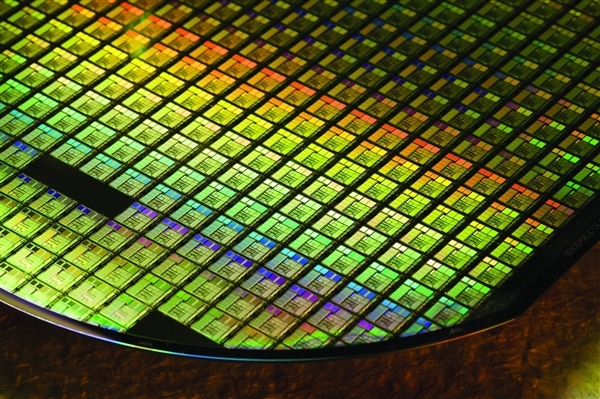

图 | 历代工艺示意图

在这种情况下,电子很容易通过隧穿效应穿透绝缘层,使器件无法正常工作。

这样的漏电不仅白白浪费了电能,更是引起芯片严重发热的原因,同时也解释了一些芯片为什么功耗过高。

而在这样的前提之下,如果芯片设计商在设计环节继续“翻车”,那么最终结果就是诞生出“火龙888”这样高功耗的产品。

正是因为这样的不确定性与各种悲观,老迈的FinFET工艺已经力不从心,但科学家们显然不会轻易放弃摩尔定律。

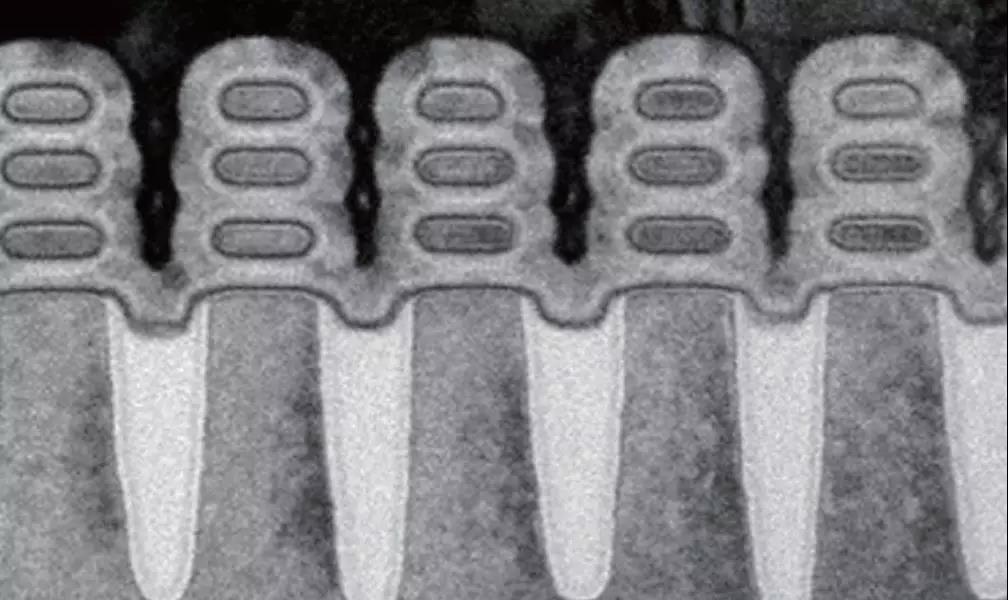

以相对成熟的三星GAA工艺(Gate-All-Around、全环绕栅极晶体管)为例,三星将原有FinFET工艺中鳍状改良成多路桥接鳍片,截面为水平板状或者水平椭圆柱状。

按照三星的说法,同样是7nm节点,使用GAA工艺可以将电压下降至0.7V,并且能够提升35%的性能、降低50%的功耗和45%的芯片面积,这还只是最初的实验品。

图 | GAA工艺横截面

除了三星的方案以外,其他几家公司也推出不同的结构:

类似nanowire的鳍片为圆柱状;其他设计包括环状、六边形状、片状等等,根据不同的场合有不同的改变。

但无论是哪种方案,理论上都是为了更好地控制电流,让先进制程成为现实。

图 | GAA工艺下,工作电压变化

万事俱备,只欠金钱?

虽然这些技术都在实验室实现了,但是距离量产还有数不清的困难。

其中最大的障碍是:钱。

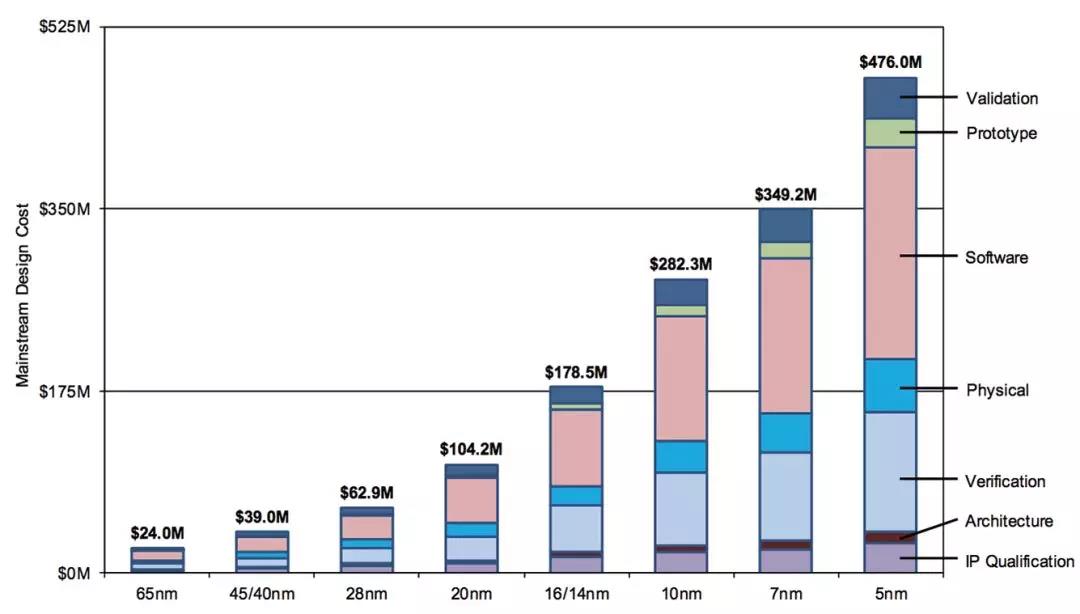

研究机构Semiengingeering曾统计了不同工艺下芯片所需费用,其中28nm节点要5130万美元投入,16nm节点需要1亿美元,7nm节点需要2.97亿美元,5nm节点需要5.42亿美元。

图 | 芯片流片的成本图

到了3nm工艺,价格直接翻到了10亿美元,更先进的2nm工艺又该花费多少呢?

摆在芯片代工厂面前的不止有物理上的摩尔定律,不为人知的摩尔第二定律也开始凸显出来:“新晶圆厂的成本每四年翻一番”。

按照台积电的说法,新建5nm工厂将需要至少投资300亿美元,就以美国凤凰城5nm工厂为例,在政府巨额补贴下,台积电仍需投资120亿美元,只要靠海运降低成本,后续依然需要不小开支。

当然,烧钱的不只是技术突破和建厂,建造2nm的配套设施同样价格不菲,比如光刻机、刻蚀机等等。

目前来说,GAA工艺要求EUV光刻机的配合,但是目前EUV光刻机还不够成熟,芯片产能和速度都不够快,因此只能做到每小时90片晶圆,但业内期望速度至少每小时125片,那么只能依靠其他工艺或是购入更多EUV光刻机,但一台EUV光刻机的价格高达1.5亿欧元,而且不是有钱就能买到的。

所以除了三星、台积电和英特尔三家厂商以外,其他厂商已经很难承受先进制程下的高额成本。

2nm何时能走出实验室?

此前,IBM曾宣布率先制造出2nm芯片,但业内人士表示“这就是在忽悠”,从设计上看依然是5nm工艺水平,只不过在命名上玩了“文字游戏”。

后来IBM解释道,他们的“2纳米”依然沿用Planar工艺的命名方式,实际上比台积电的7nm工艺有大约50%的提升,远远达不到2nm芯片的要求。

从这个小插曲就可以看出来,虽然在理论和实验室得到了验证,但2nm芯片的商业化依然离我们有些遥远。

除了钱以外,2nm工艺自身依然存在很多现实问题需要解决。

一方面是新材料,传统的硅材料是否还能坚持到2nm节点呢?

最新消息,全球顶级半导体科学家在今年的IEEE国际芯片导线技术会议上将导电性、导热性更好的石墨烯定为2nm及以下制程工艺芯片的关键材料,但事实上,碳基芯片同样需要解决成本问题。

另一方面则回到商业化的问题,芯片设计商们是否跟得上台积电和三星的节奏呢?

目前,高通骁龙和联发科虽然紧跟最新技术,但功耗控制上并不如人意;而苹果芯片又受台积电良品率限制,只能暂缓了新芯片的研发进度;三星自家芯片又体量过小,很难产生影响力。

据悉,台积电会对3nm制程量产中的问题进行改良,引入增强的N3E制程,这将成为2nm节点前的过渡工艺,这或许能让芯片设计商和手机厂商有足够的时间进行打磨。

总的来看,以目前的技术储备,2nm时代或许不再是难题。

那么到了1nm时代甚至更先进节点,科学家们还能带来什么样的惊喜呢?

最后,记得关注微信公众号:镁客网(im2maker),更多干货在等你!

硬科技产业媒体

关注技术驱动创新

FinFET工艺

IBM

南京

晶圆

高通

FinFET工艺

IBM

南京

晶圆

高通

微信ID:im2maker

微信ID:im2maker

长按识别二维码关注

长按识别二维码关注