内卷2nm?芯片三巨头的“行为艺术”罢了

一颗手机芯片,数千元?

一场关于2nm工艺的超精细(Ultra-Fine)制造竞赛,在半导体行业开启。

舞台上的主角,是台积电、三星和英特尔。

近日有媒体报道,晶圆代工巨头台积电已经开启了2nm试产的前置作业。其中在光刻计算方面,台积电紧跟AI潮流,导入了英伟达DGX H100的AI系统辅助生产,用来提升试产效率,减少能源消耗。

如果一切顺利,台积电将于今年年底前试产1000块2nm芯片,并在2025年实现大规模量产供应。

与此同时,英特尔官方高调宣布,率先在代号为“Blue Sky Creek”产品级测试芯片上实现了背面供电技术,这项为摩尔定律续命的先进技术,将在Intel 20A工艺(2nm)节点上正式落地。

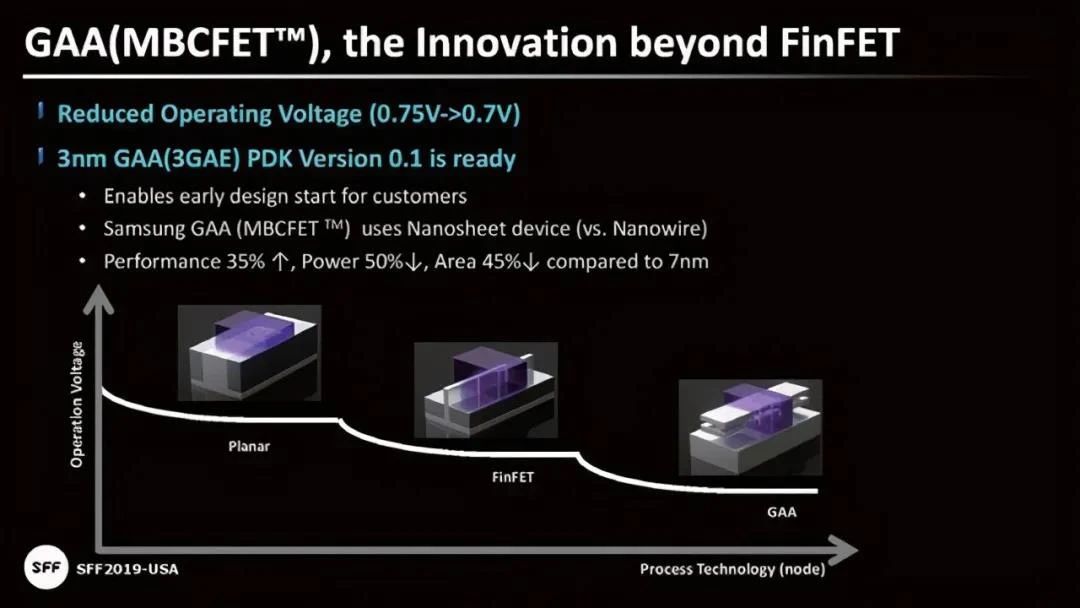

至于三星电子,其主打的GAA工艺已经在3nm节点上实现,在2nm工艺上将更加成熟。

这场半导体行业的内卷,越来越离谱了。

芯片大厂秀技术,新工艺挑战摩尔定律极限

为何芯片大厂们都这么着急2nm工艺?

简单点来说,2nm节点可以算作开启芯片制造的一个新时代,谁家技术好,自然吸引来的客户就多。

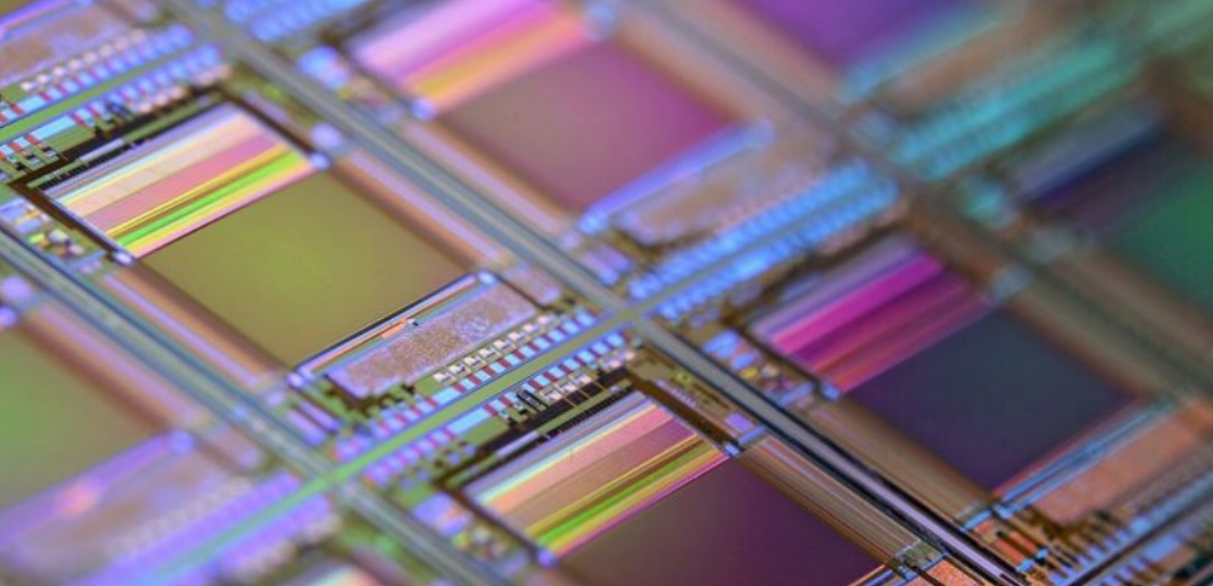

这里不得不提2nm工艺的夸张——照台积电的说法,要在指甲盖大小(100mm²)的芯片上安装490亿个晶体管,这听上去就如同天方夜谭,但工程师们总能想出新办法。

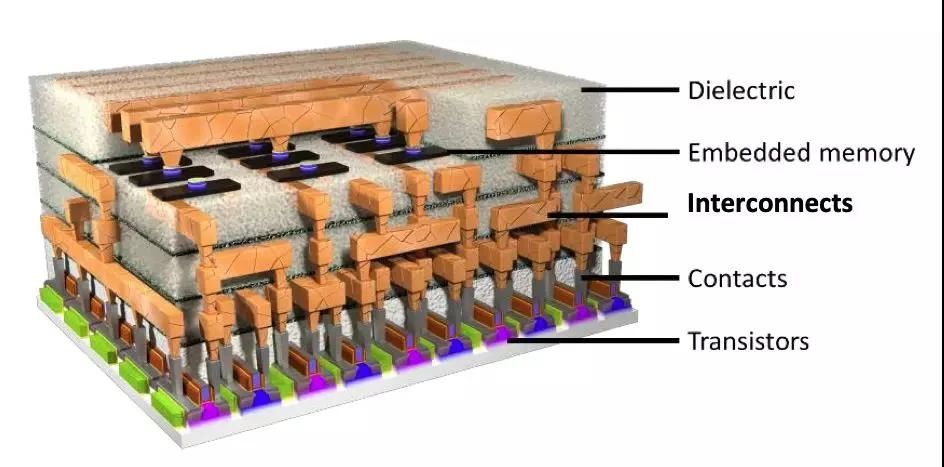

在台积电的设想里,他们希望将晶体管像积木一样堆叠起来,那么就能有效减少电路的占位面积,晶体管的密度或许就能翻倍。

这种工艺被称作nanosheet/nanowire(纳米片/纳米线)晶体管结构,早在2021年就被台积电确定用在2nm节点。

我们可以用模型来描述这种结构:在最早的Planar工艺下,半导体材料像一张2D平面的白纸;到了FinFET时代,这张白纸被折成了3D的形状(鳍(Fin)形),缩小了闸长。而进入堆叠时代,半导体材料像盖楼一样被堆叠起来,可以装下更多晶体管。

除了解决晶体管密度问题以外,新工艺另一个目的是为了解决高温以及漏电(leakage)现象。

在2nm节点,集成电路的线宽接近电子波长,精细程度几乎达到了原子级别,理论上量子隧穿效应已经来到物理极限。在这种情况下,电子很容易通过隧穿效应穿透绝缘层,使器件无法正常工作。

这样的漏电不仅白白浪费了电能,还能引起芯片严重发热,如果芯片设计商在设计环节继续“翻车”,那么最终结果就是诞生出“火龙888”这样高功耗的产品。

正是因为这样的不确定性与各种悲观,老迈的FinFET工艺已经力不从心,被抛弃已经是时间问题。

目前来看,台积电采用的nanosheet、英特尔主导的nanowire以及三星采用的GAA工艺(Gate-All-Around,全环绕栅极晶体管),本质上都是堆叠工艺。

那么堆叠工艺效果究竟如何?

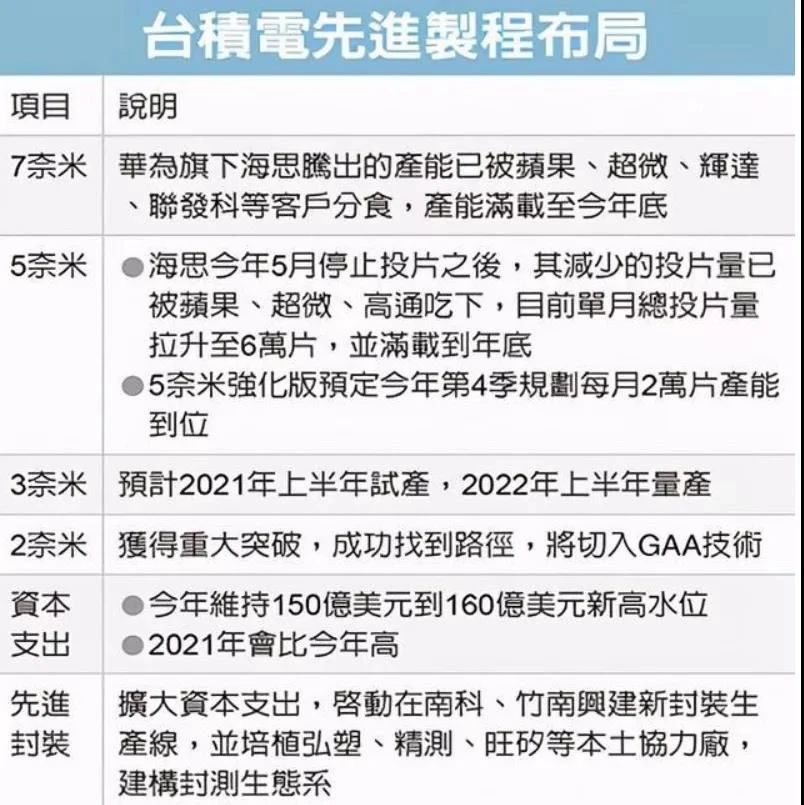

以目前较为成熟的三星GAA工艺为例,按照三星的说法,同样是7nm节点,GAA工艺可以将电压下降至0.7V,并且能够提升35%的性能、降低50%的功耗和45%的芯片面积,这还只是最初的实验品,未来的量产型号将更加强悍。

图 | GAA工艺下,工作电压变化

而除了堆叠工艺外,类似英特尔还押注了背面供电技术(PowerVia)。

顾名思义,背面供电就是将芯片上的电源线转移到晶圆空置的背面,虽然热度不及chiplet、3D堆叠,但背面供电的优势却十分明显,可以大幅应用硅片区域,同时电压降低多达7倍。

对于“寸金寸土”的晶圆来说,这项技术确实吸引力够大。

除了结构以外,三家巨头还在材料等方面带来了各种奇思妙想的方案,其目的都是摩尔定律续命,为芯片发展继续铺路。

但无论哪种方案,这些所谓的下一代技术都需要真实的产品验证,因此三家巨头们都希望能第一个推出2nm工艺,及时抢占市场。

万事俱备,只欠金钱

虽然这些技术都在实验室实现了,但是距离量产还有数不清的困难。其中最大的障碍是:钱。

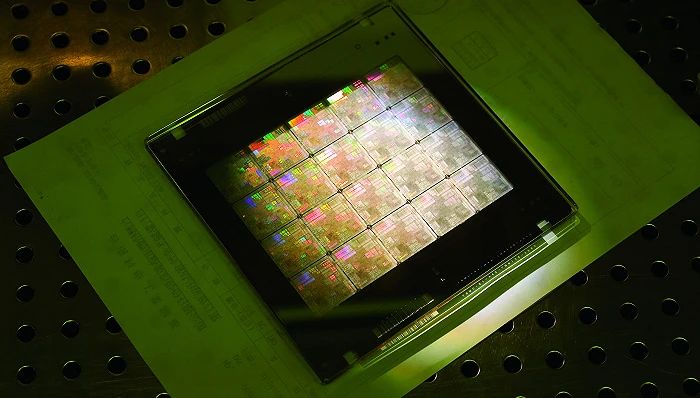

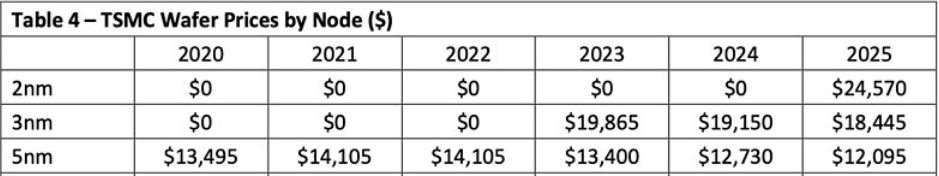

目前一颗最先进的芯片,究竟有多贵?近日,Revegnus在推特账号上曝光了台积电晶圆及先进制程芯片代工价的表单,详细列出了各类制程工艺的代工报价。

从他发布的图片来看,今年开始量产的3nm芯片,每片晶圆报价高达19865美元(约合14.1万人民币),相比5nm的13400美元,足足增长了42.9%。

图源:半导体行业观察

而这只是晶圆成本,算上掩膜、封装、测试等后期环节,一块芯片的身价可谓越来越高。

摆在芯片代工厂面前的不止有物理上的摩尔定律,不为人知的摩尔第二定律也开始凸显出来:“新晶圆厂的成本每四年翻一番”。

按照台积电的说法,新建5nm工厂将需要至少投资300亿美元,以美国凤凰城5nm工厂为例,在政府巨额补贴下,台积电仍需投资120亿美元,即便后期能靠海运降低成本,但后续依然需要不小开支。

除了技术突破和建厂,建造2nm的配套设施同样价格不菲,比如光刻机、刻蚀机等等,例如一台EUV光刻机的价格高达1.5亿欧元,还不是有钱就能买到的。

此前,三星曾希望GAA工艺在3nm阶段就打响名声,但由于EUV光刻机的限制,芯片产能和速度都不够快,因此只能做到每小时90片晶圆,而业内期望速度至少每小时125片,最终在良品率和效率面前,GAA工艺量产计划被迫推迟。

目前来看,除了三星、台积电和英特尔三家厂商以外,其他厂商已经很难承受先进制程下的高额成本。在这种情况下,其他芯片厂已经不存在进军2nm的可能性了。

这里就不得不提一下目前日本网红半导体企业Rapidus公司——这家被称作“半导体梦之队”的新企业不仅有8家日本顶级企业合资打造,同时号称已经拥有了EUV光刻机。

但在最关键的资金上,这家公司却依然等着日本政府的补贴——据介绍,光是2nm的技术,确立就需要2万亿日元,而筹备量产线还需要3万亿日元,此外在招聘半导体人才上,又需要一大笔资金。

而8家日企共同出资不过73亿日元(约 3.76 亿元人民币),即使加上日本政府提供的700亿日元(约36.05 亿元人民币)补助金作为研发预算,这样的数额远远不够。

因此日本想弯道超车2nm工艺,几乎是不可能的任务。

一场行为艺术

总的来说,2nm芯片的最终价格只会越来越高,对于消费者来说,这可不是什么好消息。

目前来看,手机、显卡是先进制程的主要应用场景,而桌面级CPU、车机芯片等领域还在使用更为成熟的老工艺。

但这两个行业恰恰处在下行周期,厂商们需要考虑如何提升销量,搭载最先进芯片的旗舰产品只是手段之一,想走量还是需要一些性价比产品。

至于头显会是未来2nm芯片的主力军吗?大概率也难承担起如此高昂的成本。

因此在内卷之下,2nm工艺不过是三巨头的一次“行为艺术”罢了。

最后,记得关注微信公众号:镁客网(im2maker),更多干货在等你!

硬科技产业媒体

关注技术驱动创新

7nm

FinFET工艺

台积电

日本

测试

7nm

FinFET工艺

台积电

日本

测试

微信ID:im2maker

微信ID:im2maker

长按识别二维码关注

长按识别二维码关注