先进封装行业深度解析:发展条件已具备,高端材料成关键

国产替代正当时。

在半导体产业,摩尔定律一直驱动着行业整体向前发展:其核心内容为,集成电路上可以容纳的晶体管数目大约每经过18个月到24个月便会增加一倍。换言之,处理器的性能大约每两年翻一倍,同时价格下降为之前的一半。

然而随着芯片尺寸逐渐逼近极限,关于摩尔定律失效的质疑声越来越多,如何延续摩尔定律也成了业界巨头共同面临的难题。

对此,有人选择研发晶体管架构,有人选择寻找新型材料,还有一种方法是在不缩小尺寸的情况下使用先进封装技术提高芯片整体性能。

如今先进封装技术发展到哪里?哪有环节需要重点关注?

在近期国金证券发布的报告《先进封装发展充要条件已具,关键材料国产替代在即》一文里,分析师以高端材料为重点,介绍了先进封装的最新进展。

以下内容为报告重点内容节选:

先进封装发展充要条件均已具备

什么是先进封装:

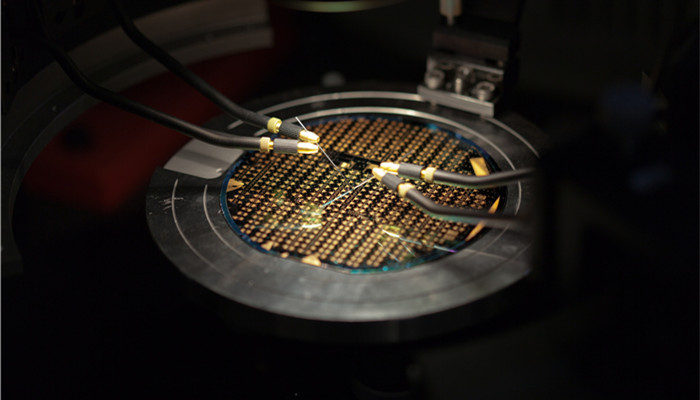

封装技术的定义为:在半导体开发的最后阶段,将一小块材料(硅晶芯片,逻辑和存储器)包裹在支撑外壳中,以防止物理损坏和腐蚀,并允许芯片连接到电路板的工艺技术。

根据定义,封装的两大关键作用:1)解决芯片如何与外界连接的问题;2)芯片隔绝保护与支撑。

研报认为:先进封装与传统封装对于半导体的作用并无二致,两者的区别在于在解决芯片与外界连接的问题上关注的重点有所不同。

具体来看:

1、传统封装技术变革的重点集中在封装主体与PCB之间的连接方案,行业解决思路仍然停留在“芯片间通信需要通过PCB走线”的层面。

2、 先进封装技术变革的重点开始转向优化芯片主体对外连接方式,最具有代表性的转变就是芯片传统对外连接方式从Wire Bonding变成了Flip Chip,这一转变提高了1级封装层面连接方式的灵活性,由此延伸出后续的2.5D/3D等高端先进封装方式。

总结来看,先进封装就是把芯片间通信问题提升至1级封装层面的技术。

为什么发展先进封装

传统封装中的芯片间通信需要经过“芯片-载体-PCB板-载体-芯片”一整套完整的流程,其中“载体”可以是TO/DIP形式的引线框架,也可以是BGA形式的封装基板,但无论是哪种载体、无论载体的性能如何提升,整个芯片通信过程所涉及的层级太多就无法完全解决通信传输信号损失的问题。

根据“两节点之间的传输损耗=传输距离*单位距离传输损耗”,传统封装的架构形式要求信号经过的路径较长,即使大幅度提升载体的性能,效率瓶颈也会很快就达到。

缩短芯片间通信距离能够大幅度提升整个功能系统效率,SoC的方案将不同芯片功能集成在一颗芯片上,使得芯片间通信在零级封装就已经完成,通信效率提升到极大水平,因此我们看到过去几年在摩尔定律的引领下,芯片制程不断演进,从而使得单芯片上晶体管数量大幅提升。

但随着多年以来摩尔定律的推进,SoC 方案的发展在设计和制造等方面都遇到了相当大的瓶颈:

1、设计瓶颈,传统的SoC是将不同类型计算任务的计算单元设计在一块晶圆上,并且每个计算单元都采用统一的工艺制程,导致SoC芯片上各个单元需要同步进行迭代,这样不仅会使得系统重构风险高,同时也会使得芯片设计成本越来越高。

2、 制造瓶颈,当前芯片工艺制程尺寸已走向极致(3nm至1nm),而1nm的宽度仅能容纳2个硅原子晶格,进一步微缩就将进入量子物理范畴,将面临量子隧穿效应等问题;

同时SoC挤进更多功能将导致芯片面积较大,从而导致良率难以提升。

除此之外还存在光刻技术难以跟进、单芯片功耗和散热问题越发突出、存储带宽难以跟进等问题,可见 SoC 制造难度正在加速上升。制造难度的提升导致摩尔定律逐步开始失效。

根据IBS的统计,芯片制程下降所带来的制造成本下降幅度已经逐步收窄,16nm到10nm每10亿颗晶体管的成本可降低31%, 而从7nm到5nm仅降低18%、从5nm到3nm仅降低4%。

在传统封装效率不足、SoC 又遭遇设计和制造瓶颈的当下,Chiplet 指导方向下的先进封装方案的发展成为了必然选择。

Chiplet俗称“芯粒”,又称为“小芯片组”,它是将多个功能单元通过封装而非晶圆制造的方式连接在一起的一种芯片异构手段,Chiplet通过先进封装的方式来实现,其可有效弥补传统封装和 SoC 的缺点。

具体来看:

1、通过1级封装显著缩短线路传输距离,较传统封装大幅度提升效率。

2、 IP复用性高,能够降低设计成本,提升迭代灵活度。

Chiplet通过将大规模SoC分解为多个小芯粒,则部分芯粒就可以做到模块化设计,一方面IP可以复用、节省设计成本,另一方面无需整个Chiplet组合统一升级、只需部分性能升级即可达到整体效能升级的作用,提升了迭代的灵活度。

工艺灵活性提升,可有效降低制造难度和成本。

原本SoC上所有功能单元需要采用统一制程来制造,但Chiplet方案下,不同单元芯粒可以分别采用不同的工艺制程制造,可有利于极大地降低芯片方案的制造成本。

因此,研报认为在传统封装和 SoC方案瓶颈问题日益突出的当下,先进封装的方案已经成为了必然的发展方向。

先进封装发展契机已现,六年复合增速将达 9.8%:

尽管Chiplet优势明显,但过去一直受制于产业客观发展因素,其一是Chiplet互联标准不统一,其二是先进封装对封装行业提出了新的技术要求,良率和产能受限是产业规模化发展的关键问题。随着产业的发展,这两大问题已经逐渐得到解决。

由此可见,先进封装已经迎来了快速发展的契机。

根据Yole预测,先进封装市场在2021~2027年间复合增长率将达到9.81%,至2027年市场规模将达到591亿美元,其中受益于AI相关的高速通信领域的发展,2.5D/3D封装将成为成长最快的板块,复合增长率将达到13.73%,至2027年市场规模将达到180亿美元。

高端材料成关键,国产替代进行时

随着先进封装技术难度提升、新增多个环节,导致工艺过程中出现了新的材料需求,并且材料 性能对先进封装工艺的影响程度大幅提升,可以说先进封装材料成为了支撑先进封装产业链发展的关键。

考虑到先进封装材料的难度高、工艺影响大、国产化率低等特点,分析师认为先进封装材料是整个产业发展中重要的投资方向。

一、临时键合(Temporary Bonding):

在传统封装中,晶圆在后续划片、压焊和封装之前需要进行背面减薄加工以降低封装贴装高度,减小芯片封装体积,改善芯片的热扩散效率、电气性能、机械性能及减小划片的加工量。

而先进封装中晶圆减薄主要是为了满足TSV制造和多片晶圆堆叠键合总厚度受限的需求,有效提高芯片制造的效率和成本效益。

由于大尺寸薄化晶圆的柔性和易脆性使其很容易发生翘曲和破损,为了提高芯片制造的良率、加工精度和封装精度,需要一种支撑系统来满足苛刻的背面制程工艺。

在此背景下,临时键合与解键合技术应运而生。此外,当前在晶圆薄化趋势持续攀升背景下,临时键合技术普及率不断提升,进而带动临时键合胶需求持续增加。

临时键合胶(Temporary Bonding Adhesive,TBA):是把晶圆和临时载板粘结在一起的中间层材料,热稳定性、化学稳定性、粘接强度、机械稳定性、均一性等是临时键合胶的关键选择因素。

临时键合胶的材料性能主要是由基础黏料的性质决定的,可用作基础黏料的高分子聚合物材料包括热塑性树脂、热固性树脂、光刻胶等。

根据新思界产业研究中心发布的《2023-2028年临时键合胶(TBA)行业市场深度调研及投资前景预测分析报告》显示,2022年全球临时键合胶市场规模约为2.2亿美元,同比增长 8.6%。其中受技术发展影响,目前全球市场由美国3M与台湾达兴材料两家企业占据主导地位,合计市场占有率已超40%,行业集中度较高。

二、RDL(重新布线层,Redistributed layer)

RDL是实现芯片水平方向电气延伸和互连,面向3D/2.5D 封装集成以及FOWLP的关键技术。

它在芯片表面沉积金属层和相应的介电层,形成金属导线,并将IO端口重新设计到新的、更宽敞的区域,形成表面阵列布局,实现芯片与基板之间的连接。

在3D封装中,如果上下是不同类型的芯片进行堆叠,则需要通过RDL重布线层将上下层芯片的IO进行对准,从而完成电气互联。

简单来说,RDL技术使设计人员能够以紧凑、高效的方式放置芯片,从而减少器件的整体尺寸。

RDL生产制造中主要用到PSPI、光刻胶、抛光材料、靶材以及一些功能性湿化学品(电镀液、清洗液、光刻胶剥离液等)。其中大部分品类都是在前道晶圆制造过程中常用的材料。

先进封装的出现使得前道材料开始应用到后道封装中,这一高端材料下沉趋势为竞争追赶者带来弯道超车机会。

1、感光性聚酰亚胺(PSPI):RDL核心材料,PSPI因具有优异的力学性能、热学性能、电学性能等,在半导体封装中被应用为缓冲层材料及再布线层材料,是关键的制程材料和永久材料。

RDL和晶圆表面的钝化层中介质通常需要光敏绝缘材料来制造,传统聚酰亚胺需要配合光刻胶使用,采用PSPI工艺流程可大幅简化。随着国内集成电路、OLED面板等产业需求的进一步扩大,国内 PSPI 的市场规模也将持续扩增。

由于 PSPI 行业技术壁垒较高,目前日本和美国企业仍占据全球 PSPI 市场的主导地位。国内方面,鼎龙股份、强力新材等已陆续实现PSPI的国产化突破。

2、光刻胶:先进封装用光刻胶与晶圆制造过程中使用的光刻胶不同,封装用光刻胶分辨率一般仅要求为微米级的厚胶、紫外光光源、436nm的g线与365nm的i线。

据集邦咨询,2022 年全球半导体光刻胶市场规模约26.4亿美元,2023年预计下滑6- 9%。目前全球高端半导体光刻胶市场主要被日本和美国公司垄断,日企全球市占率约 80%,处于绝对领先地位。目前主流厂商包括日本的东京应化、JSR、富士胶片、信越化学、住友化学,以及美国杜邦、欧洲 AZEM 等。

3、CMP材料:先进封装工艺流程中,化学机械抛光(Chemical Mechanical Polishing,CMP)是RDL、TSV工艺中的关键流程,用到的主要材料为抛光液和抛光垫。

根据SEMI数据,2022年全球半导体制造材料约447亿美元,抛光液和抛光垫分别占比4%、3%来计算,全球半导体用抛光液和抛光垫的市场空间分别为 18 亿美元和13亿美元。

抛光液市场中卡博特(Cabot)、Versum Materials、日立(Hitach)、富士美(Fujimi)、陶氏(Dow)等美日龙头厂商占据全球CMP抛光液市场近80%。

4、靶材:先进封装工艺流程中,靶材主要用于Bumping工艺中凸点下金属层及TSV工艺中电镀种子层的溅射,RDL的电镀铜中也会有工艺路线选择溅射镀Cu,从而用到靶材。

根据SEMI数据,2022年全球半导体制造材料约447亿美元,按靶材占比3%来计算,全球半导体用靶材市场空间约为13亿美元。其中日本日矿金属、东曹、美国霍尼韦尔、普莱克斯四家企业便占据了全球约80%的市场份额。

三、凸点制造(Bumping)

凸点制造(Bumping)是封装技术中关键的一环,是芯片能够实现堆叠的关键支撑。

近几年随着先进封装快速发展,从球栅阵列焊球(BGA Ball)到倒装凸点(FC Bump),再到微凸点(μBump),凸点尺寸也在不断缩小,技术难度也在不断升级。

从当前主流的高端新进封装方案中,我们可以看到 HBM、XPU以及芯片组合整个封装体对外互连时均需要用到Bumping工艺,可见Bumping在先进封装工艺中起到关键作用。

1、电镀液:Bumping中重要耗材,国内多家公司开始抢位Bumping技术的核心在于创建微小的金属凸点(bumps),用于在晶圆和封装间形成关键的电连接。而凸点间距(pitch)的精准控制在Bumping技术中至关重要,因为它直接影响到芯片内部电气信号的传输效率以及整体封装的密度,是实现高性能和高密度集成电路的关键。因此电镀液在bumping 流程中起到了关键作用。

高品质的电镀液保证了金属凸点的均匀性和可靠性。特别是在RDL(重布线层)工艺中,Bumping技术用于实现芯片与封装基板间的精确电连接。同样地,RDL技术要求高精度的凸点布局以及优异的电气性能,这些都离不开高性能的电镀液。

因此,电镀液不仅决定凸点的形成,也是确保最终产品性能和稳定性的关键。

随着半导体封装技术的发展,电镀液在传统封装到先进封装的应用中经历了显著变化。在传统封装中,电镀液主要用于形成较大的凸点(通常大于 100μm),以满足低互连密度(少于1000/mm²)和单层或少层数的封装要求,这些应用对电镀液的要求相对较低。

相比之下, 先进封装技术如3D封装和系统级封装(SiP)引入了更加复杂和细致的设计。这些技术要求电镀液支持更高的精细度,以形成更小(小于20μm)且更密集的金属凸点(超过 5000/mm²),以适应更高的互连密度和多层(多于单层)的封装需求。

这些要求不仅提升了电镀液的技术标准,包括精准的沉积控制和化学稳定性,还增加了电镀液的整体用量。

因此,在半导体行业向更高性能和更小封装尺寸的追求下,电镀液的角色在先进封装领域变得愈发重要。

在先进封装的用量及性能需求的带动下,电镀液市场有望继续成长。为满足高性能和高密度的要求,先进封装技术向更多层次的封装和互连层发展。这导致了电子器件内部更多的电镀涂层需求,从而增加了电镀液的使用。

先进封装通常涉及多层堆叠,包括多个互连层和封装层。每层都需要电镀工艺来确保良好的电连接和信号传输,增加了电镀液的用量。

同时,先进封装技术追求更高的互连密度,以实现更小的封装尺寸和更高的性能。其要求更复杂的电镀工艺以适应更多的互连通道,进一步增加了电镀液的需求。

根据Techcet 2023年8月预测数据显示,2023年全球电镀化学品市场规模将达9.92亿美元,2027 年全球电镀化学品市场规模有望达 10.47 亿美元。

目前主要玩家仍以海外为主,国内多家公司开始布局。

2、封装基板:Bumping是广义先进封装区别于传统封装的显著特征,该技术方法的推出使得芯片外延引脚数得以大幅提升,键合间距也向着更小的方向发展,这也就对作为过渡层的载板的线宽线距提出更高的要求。

对比传统封装和先进封装中形态最接近的两种封装形式WB BGA和FC BGA 可以看到,FC BGA的线宽线距能够达到 8~12um,而WB GBA最低仅能够达到25um,可见随着先进封装市场的铺开,封装基板作为关键的支撑材料也将迎来升级机会。

封装基板是封装材料中重要的组成部分,先进封装带动快速增长。封装基板作为1级封装和2级封装之间的连接层,其是整个封装制造中成本耗用最高的材料。

根据yole数据,FC BGA的成本结构中有50%来自封装基板,可见该材料的重要性。也正因如此,先进封装的发展带动了封装基板显著增长,从2017年以来封装基板的成长速度显著高于其他 PCB板类型,并且代表广义先进封装的FC类型基板的增速也相较传统封装所用的封装基板要高,预计未来封装基板市场能够保持 8%以上的复合增速,至 2026 年全球封装基板市场空间将达到214亿美元。

先进封装对封装基板的技术要求提高体现在线宽线距持续15/15um以下演进,原用于普通多层PCB的减成法工艺将不再适用,当前先进封装所用的高端封装基板普遍采用半加成法工艺制造,半加成法这种工艺和传统减成法最大的不同点就在于,不再通过现成铜箔叠层蚀刻的方式去做出线路,而是通过选择性化学沉铜/镀铜形成目标线路。

这样的工艺方式虽然省去蚀刻所带来的侧蚀问题,但对于沉铜/镀铜工艺的要求却急剧上升,在制造过程中需要解决的问题包括但不限于铜线路与低粗糙度的树脂层的结合力问题、镀铜的均匀性问题、叠孔之前的连通性问题、精细电路闪蚀等问题,技术上的挑战陡升。

在这样的技术壁垒压力下,全球封装基板主要由海外厂商垄断,特别是技术难度较高的半加成法/改进型半加成法难见国内厂商身影,我们按照2022年国内已上市的两大封装基板厂商营收数据测算,全球封装基板市场国产化率仅个位数,可见国产化率低、国产替代空间大。

四、硅通孔技术(Through Silicon Via,TSV)

硅通孔技术(Through Silicon Via,TSV)是通过导穿硅晶圆或芯片实现多层垂直互连的技术。目前TSV技术主要应用于3个方向,即垂直背面连接、2.5D封装、3D封装。

其中,垂直背面连接主要应用在CIS、SiGe 功率放大器,技术难度相对较低;

2.5D中TSV的应用体现在中介层(interposer)的硅通孔制作,服务于用作多芯片间(例如GPU与存储之间)水平连接的载体,技术难度较高;

3D封装中TSV技术的应用体现在芯片上直接进行硅通孔制作,目前常见于高带宽存储芯片(如 HBM),技术难度高。

从当前主流的高端先进封装方案来看,中介层和芯片内部硅通孔技术都已经得到广泛的应用,特别是在解决高带宽存储(存储间通信)、存储与算力芯片间通信的问题上起到关键作用。

最后,记得关注微信公众号:镁客网(im2maker),更多干货在等你!

硬科技产业媒体

关注技术驱动创新

OLED

投资

摩尔定律

日本

特征

OLED

投资

摩尔定律

日本

特征

微信ID:im2maker

微信ID:im2maker

长按识别二维码关注

长按识别二维码关注